Library Generator: Difference between revisions

Tag: Manual revert |

|||

| (10 intermediate revisions by the same user not shown) | |||

| Line 46: | Line 46: | ||

POUs can be included as hidden on the generated library. | POUs can be included as hidden on the generated library. | ||

Check "Generate as hidden" option on the POU edit properties dialog (Right click on the POU then "Edit POU properties"). | Check "Generate as hidden" option on the POU edit properties dialog (Right click on the POU then "Edit POU properties"). | ||

=== Embedded blocks === | === Embedded blocks === | ||

Embedded blocks can be declared only in Library generator folders and its subfolders. | "Embedded blocks" can be declared '''only''' in Library generator folders and its subfolders.<br> | ||

They are functions and functions blocks that do not contain any IEC code, but represent the prototype of embedded C functions published to the PLC environment from the PLC runtime.<br> | |||

[[File:embFunc.png]] | |||

=== Make libraries === | === Make libraries === | ||

| Line 56: | Line 58: | ||

=== Header files === | === Header files === | ||

Headers files are automatically generated in the same folder of the libraries.They include the functions | Headers files are automatically generated in the same folder of the libraries. They will include the C prototypes of embedded functions, embedded function blocks, and user-defined data types.<br> | ||

The header contains '''C data types''' based on the architecture of the current PLC project; in this way you can then use the generated .H files in your firmware implementation. | |||

'''Custom generation using XML config file'''<br/> | |||

If you need to customize the generated header files using your own rules, you must create a ''IEC_Embedded.xml'' file on your project folder.<br/> | |||

This file will be automatically loaded before the header generation. | |||

== | '''IEC_Embedded.xml example'''<br/> | ||

<code> | |||

<LLC> | |||

<fwHeaderGen> | |||

<options> | |||

<struprefix label="STRU" upperCase="false"/> <!-- custom prefix for generated strucutures, upper case transform --> | |||

<datafill active="yes"/> <!-- data fill for structure allignment --> | |||

<printoffs active="yes"/> <!-- address offset --> | |||

</options> | |||

<header> <!-- custom header --> | |||

myHeader | |||

</header> | |||

<footer> <!-- custom footer--> | |||

myFooter | |||

</footer> | |||

<types misrac="yes"> <!-- translation of IEC types to C types, use misrac notation --> | |||

<type iec="BOOL" c="bool_t"/> | |||

<type iec="SINT" c="int8_t"/> | |||

<type iec="USINT" c="uint8_t"/> | |||

<type iec="BYTE" c="uint8_t"/> | |||

<type iec="INT" c="int16_t"/> | |||

<type iec="UINT" c="uint16_t"/> | |||

<type iec="WORD" c="uint16_t"/> | |||

<type iec="DINT" c="int32_t"/> | |||

<type iec="UDINT" c="uint32_t"/> | |||

<type iec="DWORD" c="uint32_t"/> | |||

<type iec="REAL" c="float32_t"/> | |||

<type iec="LREAL" c="float64_t"/> | |||

</types> | |||

</fwHeaderGen> | |||

</LLC> | |||

</code> | |||

=== Export to TGT or PLL === | |||

All items inside the folder will be automatically exported to a PLCLIB as described above.<br> | |||

If you want to export them to a TGT or a PLL insted (plain IEC textual syntax) you can manually use the "Export objects to library" command, on one or more items in the folder. | |||

[[Category:LogicLab]] | [[Category:LogicLab]] | ||

Latest revision as of 11:14, 18 December 2023

FOREWORD

The purpose of this functionality is to provide, to firmware developers, the necessary tool to declare IEC blocks, including embedded ones, to be distributed as PLCLIB libraries.

Availability

The library generator feature is available on LogicLab BETA releases starting from 5.7.x.

GENERAL INFORMATION

Prerequisites

Library generation requires a ".plcprj" project with custom workspace option enabled ("Project" + "Options" + "General" + "Use customizable workspace").

Library generator folders

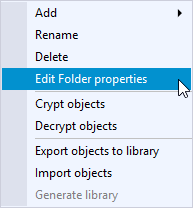

To mark a workspace folder as library generator, check the specific voice on the context menu (Right click on folder then "Edit folder properties").

Once done, a special icon appears to mark the folder.

Options

You can define some library options by editing those folder properties.

| Option | Description |

|---|---|

| Enabled | mark selected folder as library generator. |

| Version | Must be in X.Y.Z format (empty corresponds to default 1.0.0) |

| Password for encryption | Password used to crypt library content. |

| Crypt all contents | Library contents will be encrypted using the password above. |

Encrypted POUs

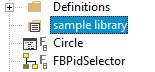

As mentioned above you can crypt all POUs contained in the library.Otherwise you can select individually each POU that has to be encrypted.

Check "Crypt with password" option on the POU edit properties dialog (Right click on the POU then "Edit POU properties").

The POU will be encrypted using the password given for the parent container folder.

Hidden POUs

POUs can be included as hidden on the generated library. Check "Generate as hidden" option on the POU edit properties dialog (Right click on the POU then "Edit POU properties").

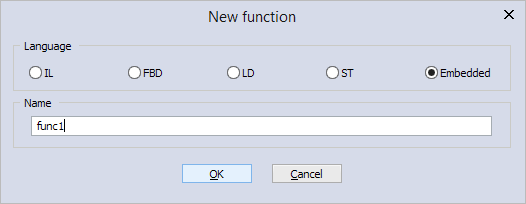

Embedded blocks

"Embedded blocks" can be declared only in Library generator folders and its subfolders.

They are functions and functions blocks that do not contain any IEC code, but represent the prototype of embedded C functions published to the PLC environment from the PLC runtime.

Make libraries

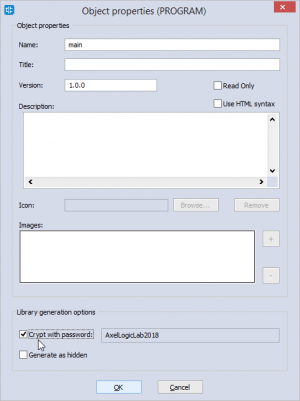

To trigger the libraries generation select "Generate library" on selected folder or "Generate libraries" of project root.

All libraries are created, in .PLCLIB format, on the PRJPATH/AutoGenerated libraries folder.

Header files

Headers files are automatically generated in the same folder of the libraries. They will include the C prototypes of embedded functions, embedded function blocks, and user-defined data types.

The header contains C data types based on the architecture of the current PLC project; in this way you can then use the generated .H files in your firmware implementation.

Custom generation using XML config file

If you need to customize the generated header files using your own rules, you must create a IEC_Embedded.xml file on your project folder.

This file will be automatically loaded before the header generation.

IEC_Embedded.xml example

<LLC>

<fwHeaderGen>

<options>

<struprefix label="STRU" upperCase="false"/>

<datafill active="yes"/>

<printoffs active="yes"/>

</options>

<header>

myHeader

</header>

<footer>

myFooter

</footer>

<types misrac="yes">

<type iec="BOOL" c="bool_t"/>

<type iec="SINT" c="int8_t"/>

<type iec="USINT" c="uint8_t"/>

<type iec="BYTE" c="uint8_t"/>

<type iec="INT" c="int16_t"/>

<type iec="UINT" c="uint16_t"/>

<type iec="WORD" c="uint16_t"/>

<type iec="DINT" c="int32_t"/>

<type iec="UDINT" c="uint32_t"/>

<type iec="DWORD" c="uint32_t"/>

<type iec="REAL" c="float32_t"/>

<type iec="LREAL" c="float64_t"/>

</types>

</fwHeaderGen>

</LLC>

Export to TGT or PLL

All items inside the folder will be automatically exported to a PLCLIB as described above.

If you want to export them to a TGT or a PLL insted (plain IEC textual syntax) you can manually use the "Export objects to library" command, on one or more items in the folder.